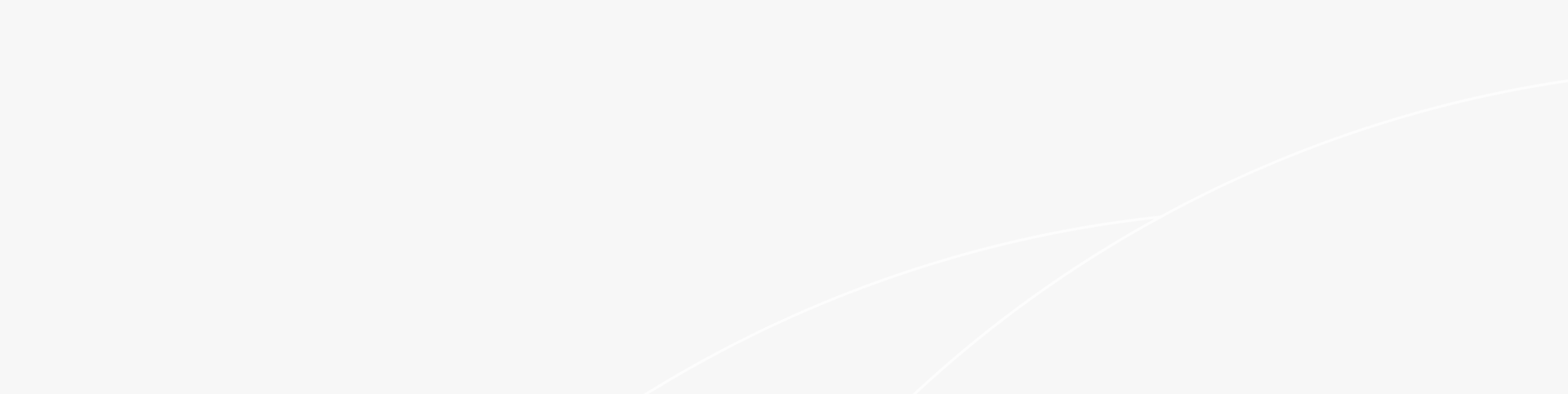

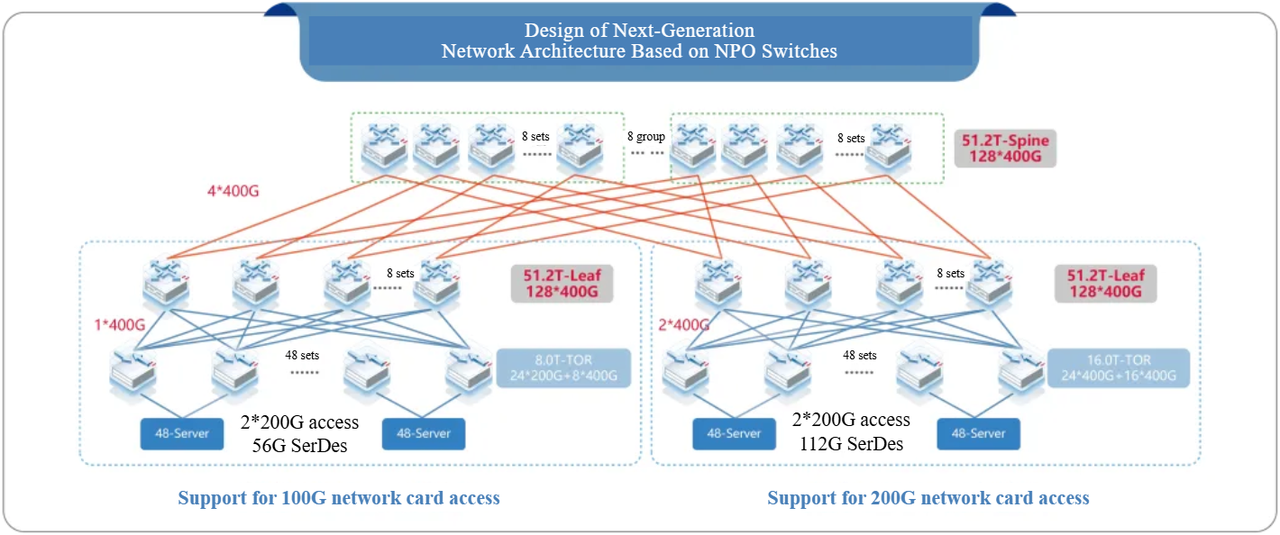

In addition to the direct demands from the business sector, enhancements to various facilities within the data centre to satisfy functional requirements are also indirectly influencing the advancement of network equipment. For instance, GPU servers utilizing the next-generation H100 necessitate a network access bandwidth of 400G; furthermore, the next-generation CX7 smart network card requires that the network access switch supports PAM4-112G SerDes (Serializer / Deserializer).

Driven by the dual imperatives of business needs and hardware innovation, the upgrading of the data centre network architecture is essential. To achieve this iteration, the technologies at three levels—switching chips, SerDes, and optical modules—must advance in a coordinated manner, as each component is integral to the overall process. It is evident that this trajectory of technological evolution will encounter numerous challenges, with power consumption being a particularly complex issue to address.

Commencing with the evaluation of switch chips that influence switch performance, it is observed that advancements in switch chip technology have led to a reduction in power consumption per bit. However, concomitant with the increase in switching bandwidth, the aggregate power consumption of switch chips utilized in data centres continues to rise annually. In addition, to switch chips, serializer - deserializer (SerDes) circuits and optical modules significantly contribute to the escalating power consumption. Data analysis reveals that the overall power consumption of a single switch in 2022 is 22 times greater than that of a single switch in 2010. Additionally, the power consumption associated with SerDes chips has amplified by a factor of 25, while the power consumption of optical modules has increased by 26 times.

The technological advancements of traditional pluggable optical modules are insufficient to support the sustainable development of data centres, which can be primarily observed in four critical areas:

The realization of signal integrity (SI) encounters significant material bottlenecks. In the context of high-speed telecommunications signal transmission via printed circuit boards (PCBs), the utilization of traditional pluggable optical modules presents challenges related to signal transmission distance and loss. The extended transmission distance contributes to notable signal degradation, posing significant obstacles to achieving robust signal integrity. Additionally, the development of lower-loss, mass-producible PCB materials faces numerous technical challenges that impede progress.

Moreover, power consumption presents another critical issue. A fully loaded 1.6T module device exhibits substantial power demands, which complicates heat dissipation design, including associated requirements for cabinet power supply. The escalation of power consumption leads to a corresponding increase in total equipment costs, including supplementary expenses related to utilities such as electricity and cooling. This dynamic consequently elevates the initial investment required for network infrastructure development.

Furthermore, product design challenges arise. Systems that employ traditional pluggable optical modules necessitate intricate system designs to accommodate 128 ports, while also addressing technical concerns related to the thermal management of high-power optical modules. This complexity contributes to elevated system costs.

In summary, Ruijie Networks aims to address the power consumption challenges within the iterative data centre network architecture, which encompasses switching chips, SerDes technology, and optical module innovations. The objective is to establish the next generation of green, energy-efficient, and sustainable data centres. By leveraging customer business scenarios and product practices, Ruijie Networks presents innovative solutions and technical recommendations for sustainable data centre networks, organized into three distinct layers.

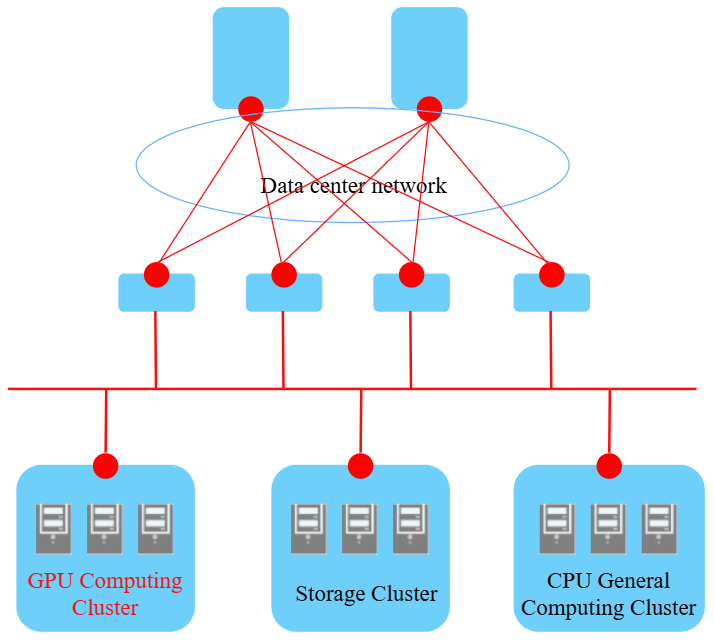

The foundational layer focuses on architecture upgrades grounded in next-generation chips, SerDes, and optical module technologies to facilitate iterative enhancements of the network architecture, thereby accommodating the ever-growing bandwidth requirements of applications such as artificial intelligence and machine learning. Building upon these architectural upgrades, the initiative begins with network devices to address the existing power consumption issues associated with SerDes and optical modules. It is essential to recognize that these challenges are not exclusively confined to the current generation; every future generation of network architecture will inevitably confront similar issues. Consequently, it is imperative to envision a sustainable development trajectory for data centre networks that prioritizes cost-efficiency and low power consumption.

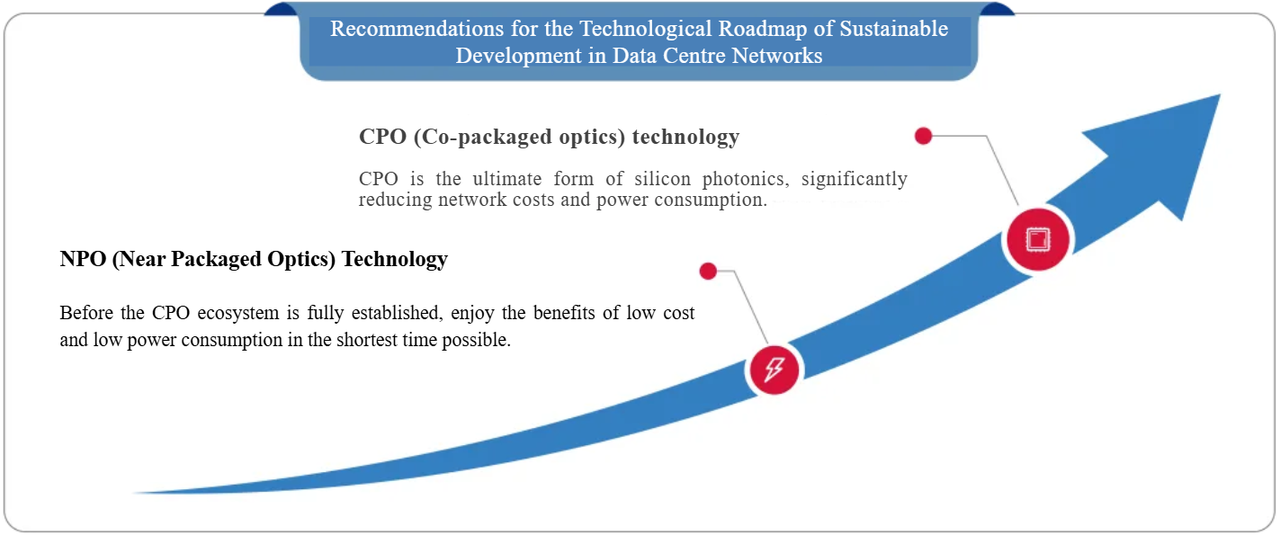

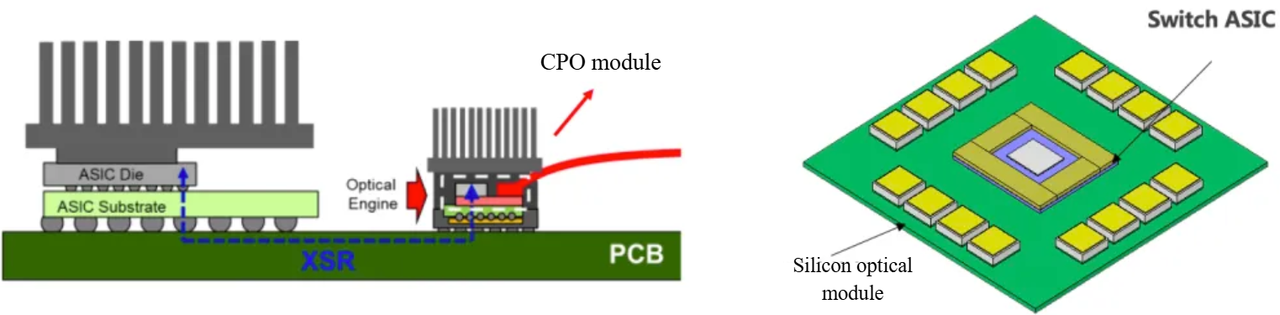

The optical engine is responsible for the optoelectronic conversion function within the switching network, with the most prevalent configuration being pluggable. As technology has advanced, new product forms have emerged. The Chip-Optical Engine Co-packaged form (CPO) integrates the switching chip and the optical engine into a unified socketed configuration, thereby facilitating a co-packaging of the chip and module. Conversely, the Non-Packaged Optical form (NPO) involves the decoupling of the optical engine from the switching chip, with both components being assembled onto the same system motherboard. While both configurations contain optoelectronic modules, the differing package positions result in variations in wiring distance and associated power consumption.

The NPO architecture represents an alternative implementation for switch systems, leveraging silicon photonics technology. Its high level of integration and open ecosystem facilitates significant advantages in both cost and power consumption. The fundamental principle of the NPO architecture is the decoupling of the optical engine from the chip within a standardized framework, achieved by mounting both components on a common motherboard via a standardized optical engine interface. This arrangement permits the flexible selection of the switching chip and the NPO module. While the NPO architecture may not realize the same degree of savings in power consumption and costs as the CPO architecture, it offers enhanced openness. As the NPO industry chain evolves, the introduction of commercial CPO modules is anticipated by 2024. Ruijie Networks, a participant in the Optical Internet Foundation (OIF), is actively engaged in exploring and developing NPO switch technology.

In November 2021, Ruijie Networks was honoured to be invited to participate in the global Open Compute Project (OCP) summit. During this prestigious event, Ruijie Networks officially unveiled its 25.6T silicon photonic NPO cold plate liquid cooling switch, designed to meet the stringent reliability standards of data centres and carrier networks.

Ruijie Networks has developed a 25.6T silicon photonic NPO cold plate liquid cooling switch, leveraging the latest 112G SerDes switching chip technology. This switch features a high-density port configuration that accommodates 64 ports operating at 400G, all within a 1RU form factor, facilitated by its 64 connectors. The system is structured with sixteen 1.6T (4×400G DR4) NPO modules, supporting eight ELS/RLS (external laser source modules). A notable advancement includes the reduction of wiring distance from the ASIC to the optical module on the printed circuit board (PCB) by 60% to 70%, thereby significantly enhancing high-speed signal integrity.

The overall architecture of the device incorporates an x86 CPU along with a 3+1 fan module and a 1+1 power module for redundancy. Furthermore, the core zone utilizes cold plate cooling technology with non-conductive liquid, which mitigates the risks of leakage and short circuits. This innovation provides robust support for the sustainable development of data centre networks.

Featured blogs

- CXL 3.0: Solving New Memory Problems in Data Centres (Part 2)

- Ruijie RALB Technology: Revolutionizing Data Center Network Congestion with Advanced Load Balancing

- Multi-Tenant Isolation Technology in AIGC Networks—Data Security and Performance Stability

- Multi-dimensional Comparison and Analysis of AIGC Network Card Dual Uplink Technical Architecture

- A Brief Discussion on the Technical Advantages of the LPO Module in the AIGC Computing Power Network